Analog Devices Unveils News Software Defined Radio Solutions

Analog Devices, Inc. today introduced a revolutionary solution for software defined radio (SDR) applications, the new AD9361 RF Agile Transceiver.

The AD9361 is supported by a wide range of design resources to expedite time to market including a software design kit and FPGA mezzanine card (FMC) to rapidly develop software defined radio solutions. It will be showcased at the upcoming ITEBiz Expo to be held in Bangalore between October 22-24, 2013.

“The AD9361 Agile Transceiver is a complete RF transceiver solution on a single chip – it’s an RF architect’s dream device,” said Matt Ettus, President of Ettus Research™, National Instruments Company.

“We combined the AD9361, with a Xilinx Spartan-6 FPGA, USB 3.0 interface and comprehensive software support, to create one of the industry’s easiest-to-use and most flexible software-defined radio solutions,” Ettus added.

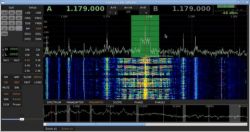

The AD-FMCOMMS2-EBZ-FMC board provides designers with a rapid prototyping environment that supports multiple communications protocols, including most licensed and unlicensed bands.

Operating over a frequency range of 70 MHz to 6 GHz, the AD9361 is a complete radio designthat combines multiple functions in a single chip. The RF agile transceivers integrate an RF front end, flexible mixed-signal baseband section, frequency synthesizers, two analog-to-digital converters and two direct conversion receivers to simplify design and reduce bill of material cost. The AD9361supportschannel bandwidth from less than 200 kHz to 56 MHz, and is highly programmable, offering the widest dynamic range available in the market today.

Two independent direct conversion receivers have a state-of-the-art noise figure and linearity. Each receive subsystem includes independent automatic gain control, dc offset correction, quadrature correction, and digital filtering, eliminating the need for these functions in the digital baseband. The AD9361 also has flexible manual gain modes that can be externally controlled.

Two high-dynamic-range A/D converters per channel digitize the received I and Q signals and pass them through configurable decimation filters and 128-tap FIR filters to produce a 12-bit output signal at the appropriate sample rate.The transmitters use a direct conversion architecture that achieves high modulation accuracy with ultra-low noise.